a free ISA, by the UC Berkeley with available open source cores for education purpose and product development.

"No recent activities."

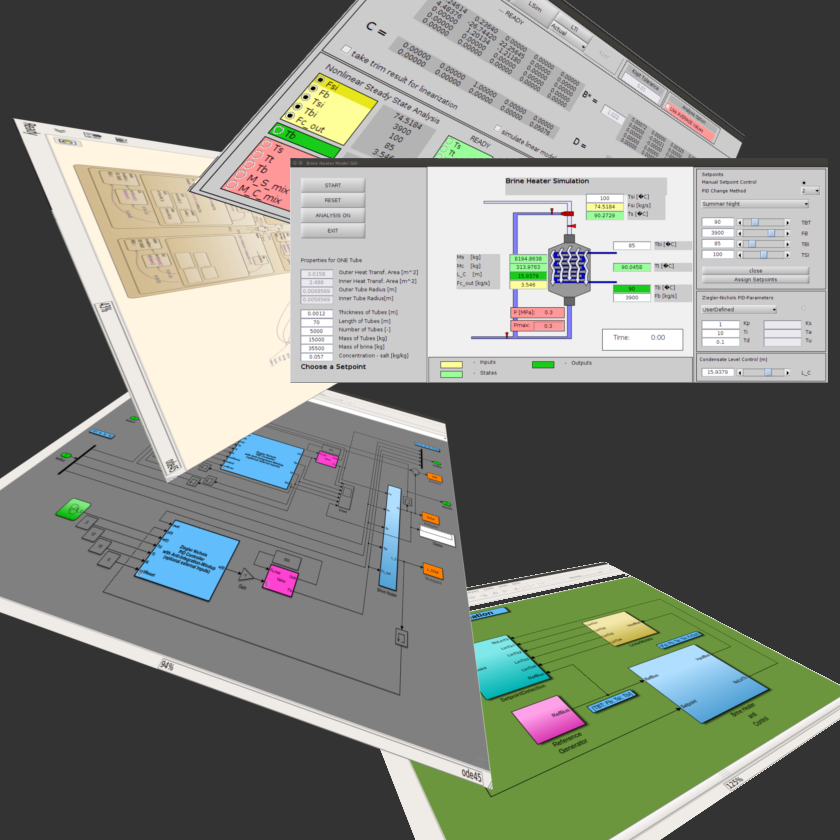

"Hybrid modelling and control for a Brine Heater of a Multi-Stage-Flash desalination plant implemented with Matlab."

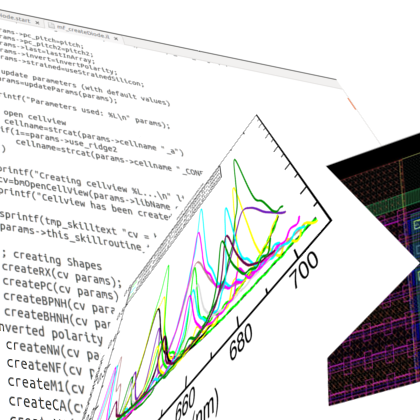

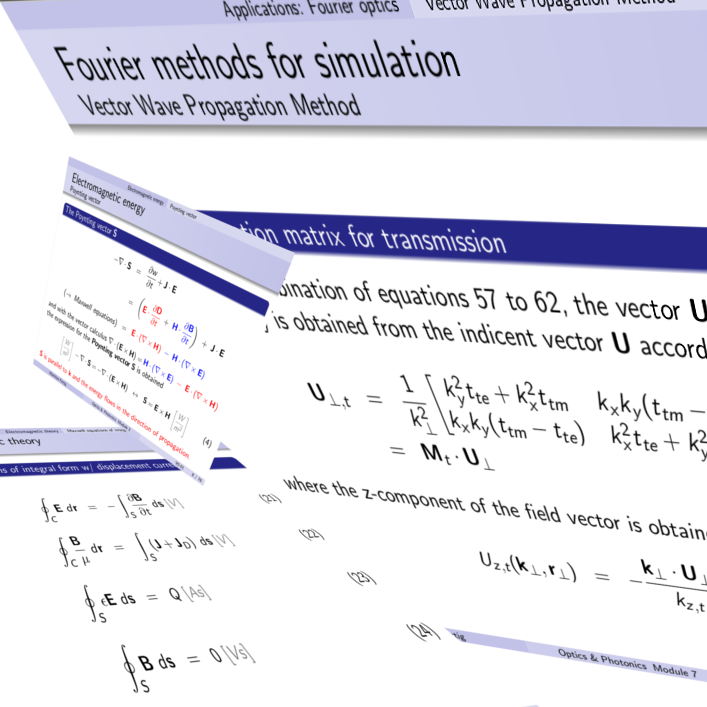

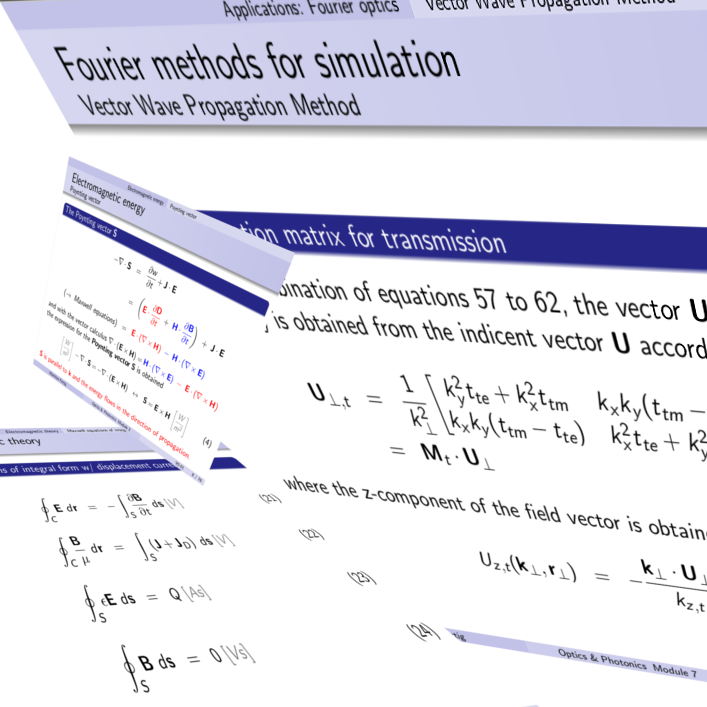

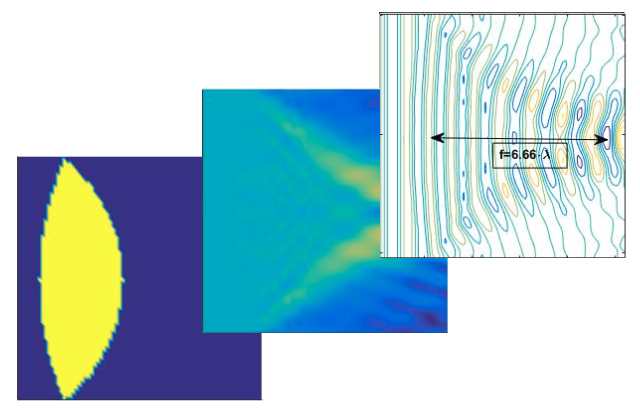

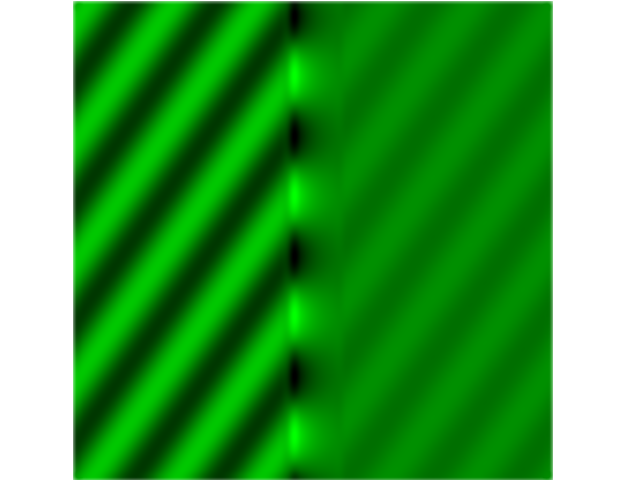

"EM simulation with CUDA/C/C++/QT, Matlab and Delphi."

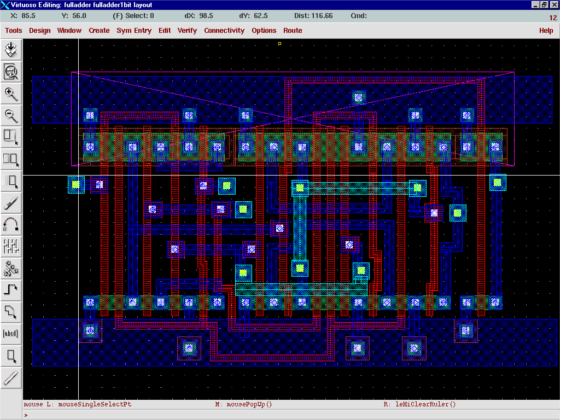

"SOI detector layout example in SKILL."

"List of open and completed bachelor and master thesis and internships."

As an academic organization and user of a Cadence academic license agreement, we hereby make our work visible.

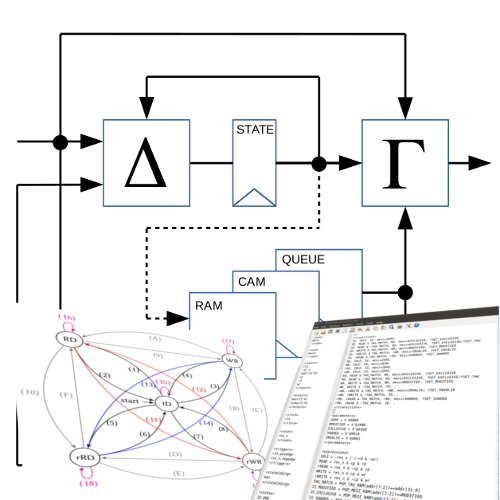

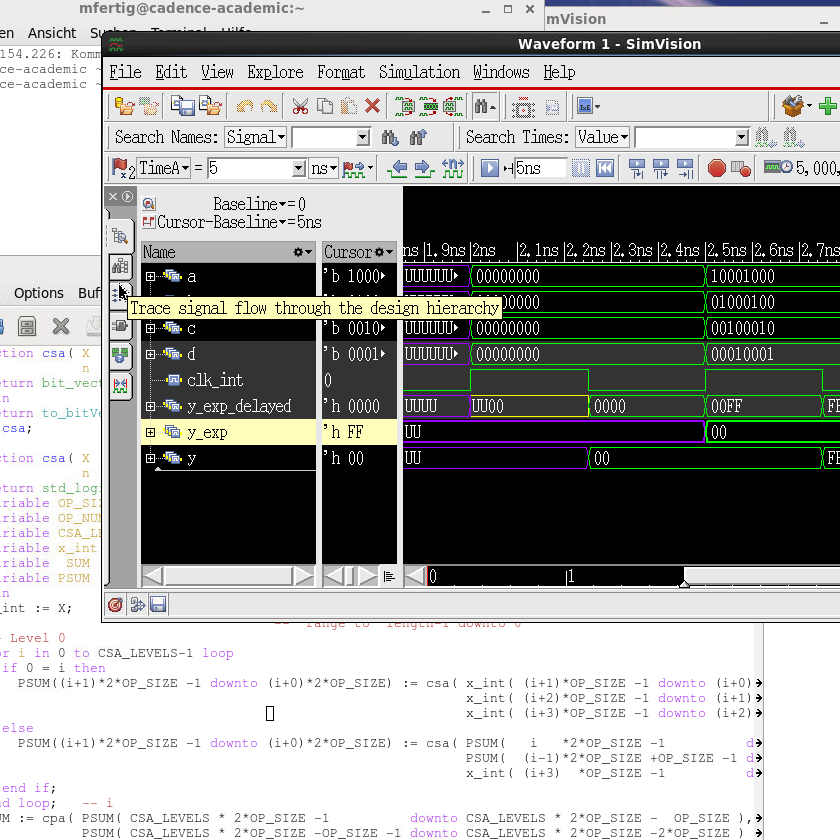

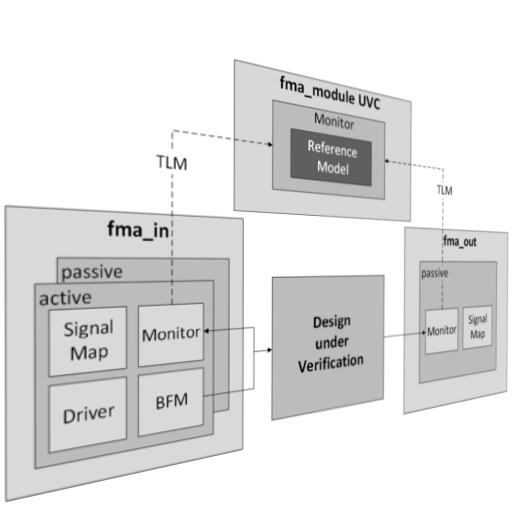

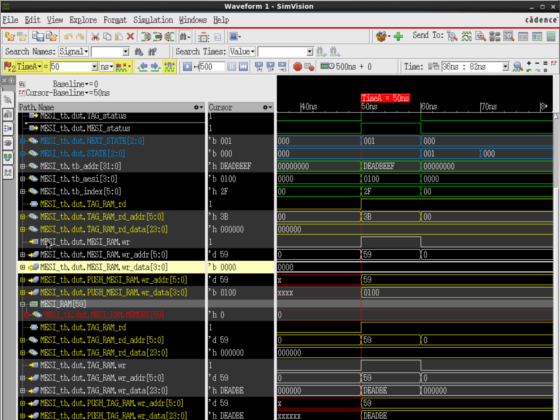

The ASIC design environment is used for educational purposes in lectures and student laboratories. Digital ASIC design is performed with the Cadence framework.

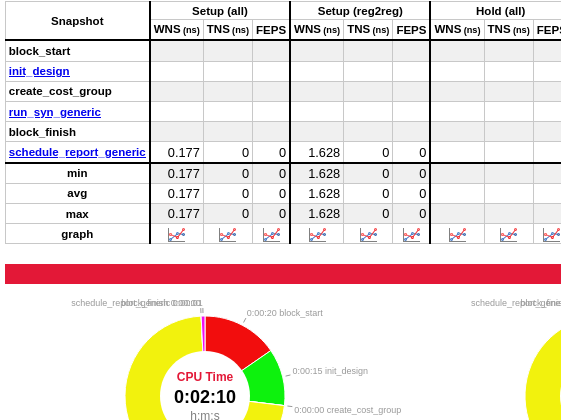

Students are trained on the front end design with HDL (VHDL or Verilog), simulation with INCISIVE, synthesis with GENUS and static timing analysis with TEMPUS.

Power Management ICs for mobile devices …

Compact Wheel Loaders in the small and mid-size range …

Microprocessor design for P- and Z-Series …