Screenshots

| Name of the course | Online | Lecture | Exercises | Lab |

|---|---|---|---|---|

| SystemVerilog for Verification | ✓ | ✓ | ✗ | ✓ |

Preliminary courses:

Recommended Preliminary courses:

Follow-on courses:

'SystemVerilog for Verification' introduces the verification extensions of SystemVerilog, Specman and the e-Language. This course is barrier-free and offered in a virtual classroom. Students visit the lecture hall or attend from home according to their individual preferences.

The course is recommended for students with a background in Object-Oriented Programming.

The course introduces to the general verification principles and techniques. In the practical exercises students develop small verification environments for functional modules and set up verification plans. The lectures are aligned to the book 'SystemVerilog for Verification' by Spear and Tumbush, 2012.

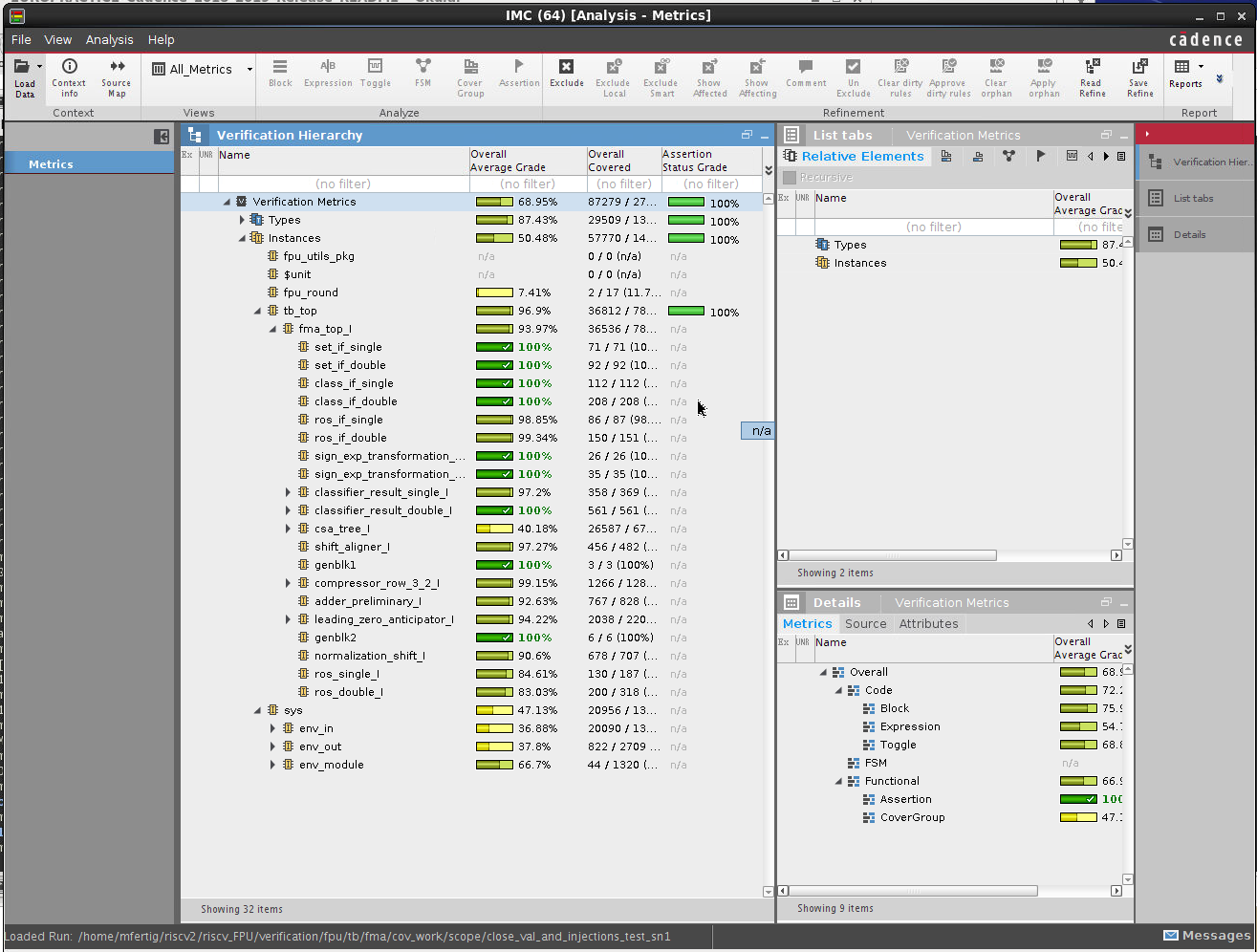

The fundamental exercises utilize a set of free tools, i.e. the Verilator C/C++ simulator and coverage analyzer and the GTKwave waveform viewer. Advanced exercises utilize the Cadence Verification Environment, Specman and the e-Language. Participants work on a given case study to understand the structure of a complex layered verification environment [w3].

| Part | Content | File |

|---|---|---|

| Student Guidance | [PDF] | |

| 1 | Introduction to the Verification Methodology - Methodology Basics, Testbench Functionality, Randomization, Coverage, Performance | [PDF] |

| 2 | Verification with SystemVerilog - Data Types, Arrays, Methods, Types and Type Conversions, User-Defined Structures, Packages, Streaming Operators, Enumeration Types | [PDF] |

| 3 | Verification with SystemVerilog - Procedural Statements, Tasks and Functions, Arguments, Local Data Storage, Simulation Time and Delay | [PDF] |

| 4 | Verification with SystemVerilog - Testbench and Design under Test, Interfaces, Stimulus, Driving and Sampling, Simulator Program, ATM-Router Example | [PDF] |

| 5 | Verification with SystemVerilog - Object Oriented Programmin with SystemVerilog, Building a Testbench | [PDF] |

| 6 | Verification with SystemVerilog - Introduction to Randomization, Constraints, Probabilities, Constraint Blocks, Randomization Problems, Random Scenarios, Random Device Control, Common Problems, Tips and Tricks | [PDF] |

| 7 | Verification with SystemVerilog - Working with Threads, Events, Semaphores, Testbench with Threads and IPC | [PDF] |

| 8 | Verification with SystemVerilog - Functional Coverage, Types of Coverage, Strategies, Simple Functional Example, Analyzing Coverage Data | [PDF] |

| 9 | Introduction to Specman and the e-Language | -* |

| 10 | Case-Study: Constrained random verification of an IEEE-754 floating point design with SystemVerilog, Specman and the e-Language | -* |