# HIMG Tonstanz

# 2019

Dieser Jahresbericht informiert über die Forschungs- und Entwicklungsarbeiten, die ich neben meinem Lehrauftrag als Professor für Digitale Systeme an der HTWG Konstanz durchführe.

- S.1 Universelle Speicherautomaten

- S.2 Massiv-Parallele optische Simulation

- S.3 Virtuelles Photoniklabor

- S.4 High-Tech-Strategie: Das Projekt SEPIA

- S.5 Digitale Prozessorentwicklung

### Universelle Speicherautomaten

und das Entwicklungswerkzeug VERIGEN

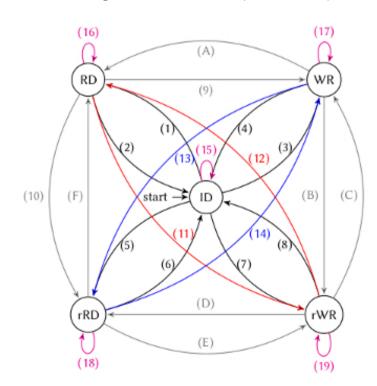

Endliche Zustandsautomaten verwenden einen Zustandsspeicher mit direkten und permanentem Speicherzugriff, um den Zustandsübergang und die Ausgabe zu bestimmen. Da viele Problemstellungen eine andere Speicherorganisation (z.B. RAM, CAM) nutzen, ist der einfache Zustandsspeicher nicht ausreichend, um derartige Problemstellungen effizient zu implementieren. Das Konzept der Universellen Speicherautomaten (UMA, Fertig 2019), erweitert Endlichen Zustands- und Kellerauto-

Erweiterte Transition des universellen Speicherautomaten.

maten um weitere Speicherkonzepte, z.B. Queue, Random Access Memory (RAM), Content Addressable Memory (CAM) und weitere. Dazu wurde die Theorie die Endlichen Zustands- und Kellerautomaten um die benötigten Speicherzugriffsmöglichkeiten erweitert, sodaß Speicherinhalte einer oder mehrerer gleichzeitiger Speicherzugriffe beim Zustandsübergang und der Ausgabe berücksichtigt werden können. Das Konzept wurde für eine Teilmenge der genannten Speicherkonzepte im Rahmen einer Bachelorarbeit untersucht und die Arbeit mit dem MLP-Leistungepreis ausgezeichnet. UMAs ermöglichen eine effiziente Implementierung komplexer Algorithmen, die unterschiedlichste Speicherkonzepte nutzen. Die Zustandsgraphen des UMA lassen sich automatisiert in die Hardwarebeschreibungssprachen (HDL) Verilog übersetzt. Mit dem entwickelten Werkzeug VERIGEN wurden universelle Speicherautomaten am Beispiel eines Cache-Kohärenz-Protokolls getestet. Derartige Protokolle kommen in Mikroprozessoren zur Verwaltung von hierarchischen Speicherkonzepten zum Einsatz.

Zustandsgraph des universellen Speicherautomaten für ein Cache-Kohärenz Protokoll (MESI-Protokoll).

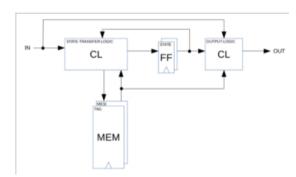

Sequentielles Schaltwerk für universelle Speicherautomaten (UMAs).

VERIGEN liefert synthetisierbare HDL auf Register Transfer Ebene (RTL) und generiert eine einfache Verifikationsumgebung für beuntzerdefinierte Tests. Eine freie Version des Entwicklungswerkzeugs ist online verfügbar. Den Studenten fortgeschrittener Kurse steht das Entwicklungswerkzeug für die praktische Umsetzung der erlernten Kursinhalte zur Verfügung.

Optif & Photonia

# Massiv-parallele optische Simulation

Die Vector Wave Propagation Methode auf einer GPU

Die Vector Wave Propagation Method (VWPM, Fertig 2011), ist ein 3D-Berechnungsverfahren auf Basis der Fourieranalyse elektromagnetischer Vektorfelder zur Berechnung der Ausbreitung elektromagnetischer Felder in inhomogenen Medien, vorzugsweise für Systeme mit optischer Achse. Im Vergleich zur Finite Difference Time Domain Methode (FDTD) oder der Rigorous Coupled Wave Analysis (RCWA) zeigt die VWPM Vorteile hinsichtlich Laufzeit und Speicherbedarf bei vergleichbarer Genauigkeit.

3D-Verteilung komplexer Brechungsindize definiert das zu simulierende System.

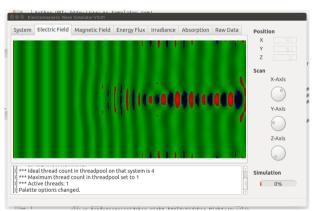

Die Vector Wave Propagation Method (VWPM, Fertig 2011), ist ein 3D-Berechnungsverfahren auf Basis der Fourieranalyse elektromagnetischer Vektorfelder zur Berechnung der Ausbreitung elektromagnetischer Felder in inhomogenen Medien, vorzugsweise für Systeme mit optischer Achse. Im Vergleich zur Finite Difference Time Domain Methode (FDTD) oder der Rigorous Coupled Wave Analysis (RCWA) zeigt die VWPM Vorteile hinsichtlich Laufzeit und Speicherbedarf bei vergleichbarer Genauigkeit. Da die Beam Propagation Method (BPM) keine exakten Berechnungen für Vektorfelder zulässt und die Wave Propagation Method (WPM) auf skalare unidirektionale Berechnungen begrenzt ist, liegt mit der VWPM eine effiziente Methode zur Berechnung bidirektionaler vektorieller Feldausbreitung ohne Winkelbeschränkung für komplexe Systeme vor, z.B. bestehend aus unterschiedlichen optischen Bauelementen, bei denen die FDTD und RCWA aus Gründen von Rechenzeit und Speicherbedarf nicht einsetzbar ist. Um die Rechengeschwindigkeit der genannten Fourier-analytischen Methoden zu erhöhen, wurde die WPM für 2D- und 3D-Systeme in einem ersten Schritt auf eine Graphics Processing Unit (GPU) portiert.

Grafische Schnittstelle zur Simulation mit der Vector Wave Propagation Method (VWPM), programmiert in C++/Qt.

Durch die Portierung von sog. Simultaneous Mult Threading (SMT) auf einer Central Processing Unit (CPU) mit mehreren Rechenkernen auf eine massiv-parallele Architektur (GPU), lassen sich signifikante Verbesserungen in der Rechengeschwindigkeit erzielen. Dabei wird das zu berechnende System zunächst in den Speicher der Grafikkarte geladen und die Feldverteilung dann auf tausenden von parallel arbeitenden Recheneinheiten zeitgleich berechnet. In ausgewählten Kursen können Studenten die nötigen theoretischen und praktischen Fähigkeiten erwerben und in interessanten Bachelor- und Masterarbeiten anwenden

http://www-home.htwg-konstanz.de/~MFERTIG/pages/gpu.html http://www-home.htwg-konstanz.de/~MFERTIG/pages/coptics.html http://www-home.htwg-konstanz.de/~MFERTIG/files/tools/gpu\_wpm\_2D.bin64 http://www-home.htwg-konstanz.de/~MFERTIG/files/tools/gpu\_wpm\_3D.bin64

Prof. Dr. Matthias Fertig

#### Virtuelles Photoniklabor

#### zur Analyse und Optimierung nano-photonischer Halbleiterkomponenten

Die Entwicklung photonischer Halbleiterkomponenten erlaubt aufgrund der Größenordnungen im Nanometerbereich und des kostenintensiven Halbleiter-Entwicklungsprozesses keine mehrfachen Iterationen im Entwicklungsprozess und den Aufbau von kostenintensiven Prototypen. Die exakte Analyse der Problemstellung auf Basis der elektromagnetischen Theorie ist daher nötig, um die Funktions- und Leistungsfähigkeit der Lösung zu sichern. Dazu steht eine Auswahl von Simulationsverfahren zur Verfügung, die für die Berechnung bestimmter Problemstellungen besonders gut geeignet sind. Der Weg von der Theorie zu einem funktionsfähigen Simulationswerkzeug und einem geeigneten parametrisierten Modell der Lösung ist komplex und erfordert ein tiefes Verständnis der theoretischen Optik und Photonik sowie für die Mathematik der Lösungsverfahren.

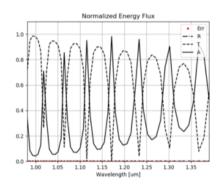

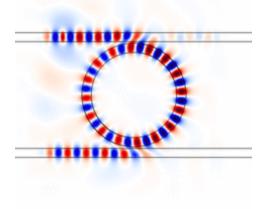

Spektralanalyse eines Ring-Resonators.

Das virtuelle Photoniklabor nutzt zwei gängige Simulationsverfahren zur Analyse und Optimierung von dreidimensionalen elektromagnetischen Feldverteilungen für ausgewählte photonische Bauelemente zu Ausbildungs- und Entwicklungszwecken. Dadurch können neue Funktionsprinzipien ohne die aufwendige und kostenintensive Entwicklungen von Prototypen untersucht werden. Das Virtuelle Photoniklabor nutzt ausschliesslich nichtkommerzielle Werkzeuge. Es kommt die Finite Difference Time Domain Methode (FDTD) sowie die Vector Wave Propagation Methode (VWPM) zum Einsatz, um z.B. Feldverteilungen und Spektralanalysen durchzuführen.

Den Studenten wird die grundlegende Theorie der Verfahren sowie die Nutzung der Simulationswerkzeuge näher gebracht. Für die Analyse und Optimierung werden parametrisierte Modelle zur Verfügung gestellt oder selbst entwickelt. Die theoretischen Grundlagen zur Optik und Photonik haben sich die Studenten idealerweise in vorangegangenen Kursen erarbeitet. Den Studenten wird jedoch auch die Möglichkeit geboten, die theoretischen Kenntnisse in weiterführenden Kursen zu erwerben.

Prof. Dr. Matthias Fertig

Schmalbandige Gauss-Welle im Ring-Resonator.

http://www-home.htwg-konstanz.de/~MFERTIG/pages/photonics.html http://www-home.htwg-konstanz.de/~MFERTIG/pages/optics.html

# High-Tech-Strategie: Das Projekt SEPIA

eine skalierbare effiziente Prozessorarchitektur für intelligente Anwendungen

Die Mikroelektronik trägt entscheidend dazu bei, die Innovationskraft Deutschlands voranzutreiben. Als führender Industriestandort benötigt Deutschland deshalb auch zukünftig umfassende Elektronik-kompetenz in Wissenschaft und Wirtschaft. Mit der Strategie des Bundesministeriums für Bildung und Forschung (BMBF) und dem Rahmenprogramm "Mikroelektronik aus Deutschland – Innovationstreiber der Digitalsierung" wird angestrebt, die Elektronikwertschöpfung in Europa bis zum Jahr 2025 deutlich zu steigern. Ein Ziel ist es dabei, neue Forschungsergebnisse in Innovationen umzusetzen, die rasch in den Anwenderbranchen zum Einsatz kommen.

Der freie Instruktionssatz RISC-V ist Grundlage des Forschungsantrags SEPIA, der für das Rahmenprogramm des BMBF eingereicht wurde. Unter der Leitung der Universität Heidelberg haben sich 13 Universitäten und Forschungseinrichtungen sowie 7 Industriepartner mit der Vision einer skalierbaren modularen Prozessorarchitektur mit Beschleunigerkomponenten für die Anwendungsgebiete Hochleistungsrechnen (HPC), Künstliche Intelligenz (KI) und Internet of Things (IoT) zu einem Projektkonsortium zusammengeschlossen und den Projektantrag SEPIA entwickelt.

Mit der Entwicklung einer skalierbaren und modularen Mikroarchitektur auf Basis eines freien Instruktionssatzes ergibt sich die Möglichkeit, ein sich seit Jahrzehnten monopolisierendes Marktgeschehen auf eine breitere Basis zu stellen und der Innovationskraft neue Impulse zu verschaffen. Die exzellente Expertise der Industriepartner in den Anwendungsgebieten und das über Jahrzehnte aufgebaute Know-How in den Grundlagen der Prozessorentwicklung, der Verbindungstechnologie und der Netzwerkarchitektur wird genutzt, um eine vielseitige Architektur zu entwickeln. Dabei soll der Open-Source Gedanke unterstützt werden und gleichzeitig die wirtschaftliche Nutzung möglich bleiben. Die RISC-V Foundation und die Nutzung der RISC-V Architektur durch junge Startup-Unternehmen in den USA übernehmen hier wieder einmal eine beispielhafte Vorreiterrolle. Geeignete Konzepte für eine Verwertung in Deutschland und der Europäischen Union sind noch zu finden.

Ende 2019 wurde vom BMBF entschieden, daß der Projektantrag SEPIA die nächste Antragsrunde leider nicht erreichen wird. Die Projektpartner werden das Geschehen jedoch weiterhin aktiv mitgestalten und beabsichtigen auch zukünftig zur Weiterentwicklung des Forschungs- und Entwicklungsstandortes Deutschland beizutragen.

Prof. Dr. Matthias Fertig

https://www.elektronikforschung.de/ https://www.bmbf.de/de/elektroniksysteme-made-in-germany-850.html https://www.hightech-strategie.de/

## Digitale Prozessorentwicklung

Verifikation einer RISC-V kompatiblem ,Double Precision Fused Multiply Add' Einheit

RISC-V, ein quelloffener und erweiterbarer Instruktionssatz gibt der Rechnerarchitektur neue Impulse für innovative Lösungen. Im Bereich des Hochleistungsrechnens (HPC) und der parallelen Rechencluster hat die Fließkommaeinheit (FPU) entscheindenden Einfluss auf die Leistungsfähigkeit. So wird die Rechenleistung in Fließkommaoperationen pro Sekunde gemessen und schnelle hocheffiziente Fließkommaeinheiten sind gerade im HPC unabdingbar.

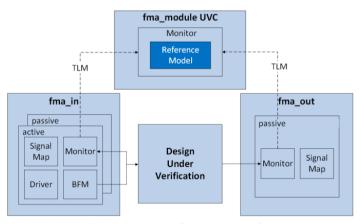

Im Rahmen einer kooperativen Masterarbeit der Universität Heidelberg und der Hochschule Konstanz wurde eine RISC-V 64 Bit Fused-Multiply-Add (FMA) Einheit mit effizientem "Single-Path' Algorithmus entwickelt und verifiziert, die pro Takt eine Multiplikation kombiniert mit einer Addition ausführen kann. Die Arbeit implementiert und verifiziert einen effizienten Datenpfad einer 64-Bit FMA Instruktion. Um die große Menge an Eingangswerten zu bewältigen, wurde die Universal Verication Methodology (UVM) und Specman e in einem simulationsbasierten und metrikgetriebenen Verifikationsansatz (MDV) genutzt. Die UVM ist industrieller Standard und bietet die Möglichkeit, Verikationskomponenten modular und wiederverwendbar zu entwerfen. In dem vorgestellten innovativen Ansatz werden zwei bewährte Referenzmodelle genutzt und wechselseitig abgeglichen. Die primäre Referenz ist die FPU des Intel-Prozessors des Verifikationssystems, die sekundäre Referenz ist die Softfloat Umgebung der Universität Berkeley. Die Verifikation läuft transaktionsbasiert ab und verwendet die Metriken 'functional coverage' und 'code coverage' in Verbindung mit den Ansätzen ,constraint random' und ,corner case' für die Generation der Stimuli. Dabei wurde stets auf Konformität zum IEEE-754 Standard und zur RISC-V Architektur geachtet. Die Analyse der Suchraumabdeckung (Coverage) liefert Hinweise auf "blinde Flecken" in der Verifikation, sodaß eine zielgerichtete Planung des Verifikationsprozess möglich ist. Die gesamte Methodik ist kompatibel zum Cadence Design Environment und kann daher alle Möglichkeiten der Planung und Analyse von Testumgebungen sowie weitere Möglichkeiten der Hardwareentwicklungsumgebung nutzen.

Struktur der Verifikationsumgebung (Quelle: F. Kaiser)

Die entwickelte Simulationsumgebung ist in der Lage, 10 Millionen Fließkommaoperationen pro Stunde gegen zwei Referenzmodelle parallel zu verifizieren. Zur Definition der Testszenarien wurde das IBM Entwicklungswerkzeug FPGen genutzt. Darin sind alle wesentlichen Tests für die unterschiedliche Instruktionen einer FPU in sogenannten Buckets organisiert. In Anlehnung an FPGen wurden die erforderlichen Tests für die FMADD Instruktion festgelegt.

In ausgewählten Kursen können Studenten die nötigen Kenntnisse und Fertigkeiten erwerben, die für die Entwicklung und Verifikation von digitalen Halbleiterkomponenten nötig sind. Dazu verfügt die Hochschule über entsprechende Entwicklungswerkzeuge.

Prof. Dr. Matthias Fertig

Konstanz, January 2020

Text und Layout: Prof. Dr. Matthias Fertig